LF155, LF156, LF256, LF257 LF355, LF356, LF357

SNOSBH0D-MAY 2000-REVISED NOVEMBER 2015

# LFx5x JFET Input Operational Amplifiers

Technical

Documents

## 1 Features

- Advantages

- Replace Expensive Hybrid and Module FET Op Amps

- Rugged JFETs Allow Blow-Out Free Handling Compared With MOSFET Input Devices

- Excellent for Low Noise Applications Using Either High or Low Source Impedance—Very Low 1/f Corner

- Offset Adjust Does Not Degrade Drift or Common-Mode Rejection as in Most Monolithic Amplifiers

- New Output Stage Allows Use of Large Capacitive Loads (5,000 pF) Without Stability Problems

- Internal Compensation and Large Differential Input Voltage Capability

- Common Features

- Low Input Bias Current: 30 pA

- Low Input Offset Current: 3 pA

- High Input Impedance: 10<sup>12</sup> Ω

- Low Input Noise Current: 0.01 pA/ $\sqrt{Hz}$

- High Common-Mode Rejection Ratio: 100 dB

- Large DC Voltage Gain: 106 dB

- Uncommon Features

- Extremely Fast Settling Time to 0.01%:

- 4 µs for the LFx55 devices

- 1.5 µs for the LFx56

- 1.5  $\mu$ s for the LFx57 (A<sub>V</sub> = 5)

- Fast Slew Rate:

- 5 V/µs for the LFx55

- 12 V/µs for the LFx56

- 50 V/ $\mu$ s for the LFx57 (A<sub>V</sub> = 5)

- Wide Gain Bandwidth:

- 2.5 MHz for the LFx55 devices

- 5 MHz for the LFx56

- 20 MHz for the LFx57 ( $A_V = 5$ )

- Low Input Noise Voltage:

- 20 nV/ $\sqrt{Hz}$  for the LFx55

- 12 nV/ $\sqrt{\text{Hz}}$  for the LFx56

- 12 nV/ $\sqrt{\text{Hz}}$  for the LFx57 (A<sub>V</sub> = 5)

## 2 Applications

Tools &

Software

- Precision High-Speed Integrators

- Fast D/A and A/D Converters

- High Impedance Buffers

- Wideband, Low Noise, Low Drift Amplifiers

- Logarithmic Amplifiers

- Photocell Amplifiers

- Sample and Hold Circuits

## **3 Description**

The LFx5x devices are the first monolithic JFET input operational amplifiers to incorporate well-matched, high-voltage JFETs on the same chip with standard bipolar transistors (BI-FET<sup>™</sup> Technology). These amplifiers feature low input bias and offset currents/low offset voltage and offset voltage drift, coupled with offset adjust, which does not degrade drift or common-mode rejection. The devices are also designed for high slew rate, wide bandwidth, extremely fast settling time, low voltage and current noise and a low 1/f noise corner.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

|             | SOIC (8)   | 4.90 mm × 3.91 mm |

| LFx5x       | TO-CAN (8) | 9.08 mm × 9.08 mm |

|             | PDIP (8)   | 9.81 mm × 6.35 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

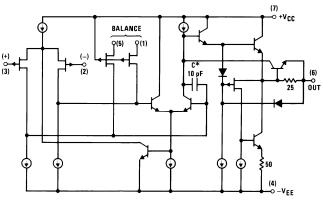

### Simplified Schematic

3 pF in LF357 series

Sample &

Buv

# Table of Contents

| 1 | Fea  | tures 1                                                                     |

|---|------|-----------------------------------------------------------------------------|

| 2 | Арр  | lications 1                                                                 |

| 3 | Des  | cription1                                                                   |

| 4 | Rev  | ision History 2                                                             |

| 5 | Pin  | Configuration and Functions 3                                               |

| 6 | Spe  | cifications 4                                                               |

|   | 6.1  | Absolute Maximum Ratings 4                                                  |

|   | 6.2  | ESD Ratings 4                                                               |

|   | 6.3  | Recommended Operating Conditions 4                                          |

|   | 6.4  | Thermal Information 5                                                       |

|   | 6.5  | AC Electrical Characteristics, $T_A = T_J = 25^{\circ}C$ , $V_S = \pm 15 V$ |

|   | 6.6  | DC Electrical Characteristics, $T_A = T_J = 25^{\circ}C$ , $V_S = \pm 15 V$ |

|   | 6.7  | DC Electrical Characteristics 6                                             |

|   | 6.8  | Power Dissipation Ratings 7                                                 |

|   | 6.9  | Typical Characteristics 8                                                   |

| 7 | Deta | ailed Description 14                                                        |

|   | 7.1  | Overview 14                                                                 |

|    | 7.2  | Functional Block Diagram          | 15   |

|----|------|-----------------------------------|------|

|    | 7.3  | Feature Description               | 16   |

|    | 7.4  | Device Functional Modes           | 16   |

| 8  | Арр  | lication and Implementation       | . 17 |

|    | 8.1  | Application Information           | 17   |

|    | 8.2  | Typical Application               | 18   |

|    | 8.3  | System Examples                   | 20   |

| 9  | Pow  | er Supply Recommendations         | . 33 |

| 10 | Lay  | out                               | . 33 |

|    |      | Layout Guidelines                 |      |

|    |      | Layout Example                    |      |

| 11 | Dev  | ice and Documentation Support     | . 35 |

|    | 11.1 |                                   |      |

|    | 11.2 | Community Resources               | 35   |

|    | 11.3 | Trademarks                        | 35   |

|    | 11.4 | Electrostatic Discharge Caution   | 35   |

|    | 11.5 | Glossary                          | 35   |

| 12 | Med  | hanical, Packaging, and Orderable |      |

|    |      | rmation                           | . 35 |

|    |      |                                   |      |

## **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| <ul> <li>Added Pin Configuration and Functions section, ESD Ratings table, Thermal Information table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section</li> <li>Removed T<sub>HIGH</sub> parameter as it is redundant to T<sub>A</sub> maximum</li> </ul> |                                                                                                                                                                                                                    | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable | 1    |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Removed T <sub>HIGH</sub> parameter as it is redundant to T <sub>A</sub> maximum                                                                                                                                   | 4    |

| CI                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | hanges from Revision B (March 2013) to Revision C                                                                                                                                                                  | Page |

2 Submit Documentation Feedback

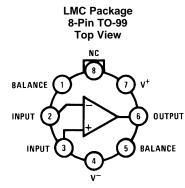

# 5 Pin Configuration and Functions

Available per JM38510/11401 or JM38510/11402

#### **Pin Functions**

| PIN     |      | I/O | DESCRIPTION                      |  |  |

|---------|------|-----|----------------------------------|--|--|

| NAME    | NO.  | 1/0 | DESCRIPTION                      |  |  |

| BALANCE | 1, 5 | I   | Balance for input offset voltage |  |  |

| +INPUT  | 3    | I   | Noninverting input               |  |  |

| -INPUT  | 2    | I   | Inverting input                  |  |  |

| NC      | 8    | —   | No connection                    |  |  |

| OUTPUT  | 6    | 0   | Output                           |  |  |

| V+      | 7    | —   | Positive power supply            |  |  |

| V–      | 4    | —   | Negative power supply            |  |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)(3)

|                                       |               |                        |                        | MIN   | MAX        | UNIT |

|---------------------------------------|---------------|------------------------|------------------------|-------|------------|------|

| Supply voltage                        |               | LF155x, LF256x, LF356B | LF155x, LF256x, LF356B |       |            | V    |

|                                       |               | LF35x                  |                        |       | ±18        | V    |

|                                       |               | LF15x, LF25x, LF356B   |                        |       | ±40        | V    |

| Differential input                    | voltage       | LF35x                  |                        |       | ±30        | V    |

| Input voltage <sup>(4)</sup>          |               | LF15x, LF25x, LF356B   |                        |       | ±20        |      |

|                                       |               | LF35x                  | LF35x                  |       | ±16        | V    |

| Output short circuit duration         |               |                        |                        | Conti | Continuous |      |

| · · ·                                 |               | I MO nankana           | LF15x                  |       | 150        |      |

| Ŧ                                     |               | LMC package            | LF25x, LF356B, LF35x   |       | 115        |      |

| T <sub>JMAX</sub>                     |               | P package              | LF25x, LF356B, LF35x   |       | 100        | °C   |

|                                       |               | D package              | LF25x, LF356B, LF35x   |       | 100        |      |

| Coldoring                             | TO-99 package | Soldering (10 sec.)    |                        | 300   |            |      |

| Soldering<br>information              | PDIP package  | Soldering (10 sec.)    |                        |       | 260        |      |

| (lead temp.)                          | 0010          | Vapor phase (60 sec.)  | LF25x, LF356B, LF35x   |       | 215        |      |

|                                       | SOIC package  | Infrared (15 sec.)     | LF25x, LF356B, LF35x   |       | 220        | 1    |

| Storage temperature, T <sub>stg</sub> |               |                        | ·                      | -65   | 150        | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The maximum power dissipation for these devices must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum available power dissipation at any temperature is P<sub>D</sub> = (T<sub>JMAX</sub> - T<sub>A</sub>) / θ<sub>JA</sub> or the 25°C P<sub>dMAX</sub>, whichever is less.

(3) If Military/Aerospace specified devices are required, contact the TI Sales Office/Distributors for availability and specifications.

(4) Unless otherwise specified the absolute maximum negative input voltage is equal to the negative power supply voltage.

## 6.2 ESD Ratings

|                    |                         |                                                                      | VALUE | UNIT |  |

|--------------------|-------------------------|----------------------------------------------------------------------|-------|------|--|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)(2)</sup> | ±1000 | V    |  |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) 100 pF discharged through  $1.5 \cdot k\Omega$  resistor

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       |        | MIN | NOM            | MAX | UNIT |  |  |

|-----------------------|--------|-----|----------------|-----|------|--|--|

|                       | LF15x  | ±15 | Vs             | ±20 |      |  |  |

|                       | LF25x  | ±15 | Vs             | ±20 | V    |  |  |

| Supply voltage, $V_S$ | LF356B | ±15 | Vs             | ±20 |      |  |  |

|                       | LF35x  |     |                | ±15 |      |  |  |

|                       | LF15x  | -55 | T <sub>A</sub> | 125 |      |  |  |

| T <sub>A</sub>        | LF25x  | -25 | T <sub>A</sub> | 85  | °C   |  |  |

|                       | LF356B | 0   | T <sub>A</sub> | 70  | C    |  |  |

|                       | LF35x  | 0   | T <sub>A</sub> | 70  |      |  |  |

## 6.4 Thermal Information

|                               |                                              |          | LF156, LF   | LF356       |          |      |

|-------------------------------|----------------------------------------------|----------|-------------|-------------|----------|------|

| THERMAL METRIC <sup>(1)</sup> |                                              | P (PDIP) | D<br>(SOIC) | LMC (TO-99) | P (PDIP) | UNIT |

|                               |                                              | 8 PINS   | 8 PINS      | 8 PINS      | 8 PINS   |      |

|                               | Junction-to-ambient thermal resistance       | 130      | 195         | —           | 55.2     |      |

| $R_{	extsf{	heta}JA}$         | Still Air                                    | —        | —           | 160         | —        | °C/W |

|                               | 400 LF/Min Air Flow                          | _        | _           | 65          | —        |      |

| R <sub>0JC(top)</sub>         | Junction-to-case (top) thermal resistance    | —        | _           | 23          | 44.5     | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | —        | _           | —           | 32.4     | °C/W |

| ΨJT                           | Junction-to-top characterization parameter   | —        | —           | —           | 21.7     | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | —        | _           | _           | 32.3     | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 6.5 AC Electrical Characteristics, $T_A = T_J = 25^{\circ}C$ , $V_S = \pm 15 V$

| P               | PARAMETER                             |                            | TEST CO                   | ONDITIONS             | MIN | TYP  | MAX                | UNIT   |  |

|-----------------|---------------------------------------|----------------------------|---------------------------|-----------------------|-----|------|--------------------|--------|--|

|                 |                                       |                            |                           | LFx55                 |     | 5    |                    |        |  |

| SR              | Claur Data                            | LF15x: A <sub>V</sub> = 1  |                           | LFx56, LF356B         | 7.5 |      |                    | 1//    |  |

|                 | Slew Rate                             |                            |                           | LFx56, LF356B         |     | 12   |                    | V/µs   |  |

|                 |                                       | LF357: A <sub>V</sub> = 5  |                           | LFx57                 |     | 50   |                    |        |  |

| 0               |                                       | LFx55                      |                           |                       |     | 2.5  |                    |        |  |

| GBW             | Gain Bandwidth<br>Product             | LFx56, LF356               | В                         |                       |     | 5    |                    | MHz    |  |

|                 | 1100001                               | LFx57                      |                           |                       |     | 20   |                    |        |  |

|                 |                                       | LFx55                      |                           |                       |     | 4    |                    |        |  |

| t <sub>s</sub>  | Settling Time to 0.01% <sup>(1)</sup> | LFx56, LF356               | В                         |                       |     | 1.5  |                    | μs     |  |

|                 | 0.0170                                | LFx57                      |                           |                       |     | 1.5  |                    |        |  |

|                 | Equivalent Input<br>Noise Voltage     | age R <sub>S</sub> = 100 Ω | f = 100 Hz<br>f = 1000 Hz | LFx55                 |     | 25   |                    |        |  |

|                 |                                       |                            |                           | LFx56, LF356B         |     | 15   |                    | nV/√Hz |  |

| •               |                                       |                            |                           | LFx57                 |     | 15   |                    |        |  |

| e <sub>n</sub>  |                                       |                            |                           | LFx55                 |     | 20   | nV/√               |        |  |

|                 |                                       |                            |                           | LFx56, LF356B         |     | 12   |                    | nV/√Hz |  |

|                 |                                       |                            |                           | LFx57                 |     | 12   |                    |        |  |

|                 |                                       |                            |                           | LFx55                 |     |      |                    |        |  |

|                 |                                       | f = 100 Hz                 |                           | Hz LFx56, LF356B 0.01 |     |      | pA/√ <del>Hz</del> |        |  |

| :               | Equivalent Input                      |                            |                           | LFx57                 |     |      |                    |        |  |

| İn              | Current Noise                         |                            |                           | LFx55                 |     |      |                    |        |  |

|                 |                                       | f = 1000 Hz                |                           | LFx56, LF356B         |     | 0.01 |                    | pA/√Hz |  |

|                 |                                       | LFx57                      |                           |                       |     |      |                    |        |  |

|                 |                                       | LFx55                      | LFx55                     |                       |     | -    |                    |        |  |

| C <sub>IN</sub> | Input<br>Capacitance                  | LFx56, LF356               | В                         |                       |     | 3    |                    | pF     |  |

|                 | Capacitanice                          | LFx57                      |                           |                       |     |      |                    |        |  |

(1) Settling time is defined here, for a unity gain inverter connection using 2-kΩ resistors for the LF15x. It is the time required for the error voltage (the voltage at the inverting input pin on the amplifier) to settle to within 0.01% of its final value from the time a 10-V step input is applied to the inverter. For the LF357, A<sub>V</sub> = -5, the feedback resistor from output to input is 2 kΩ and the output step is 10 V (See Settling Time Test Circuit).

# 6.6 DC Electrical Characteristics, $T_A = T_J = 25^{\circ}C$ , $V_S = \pm 15 V$

| PARAMETER      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------------|-----------------|-----|-----|-----|------|

| Supply current | LF155           |     | 2   | 4   |      |

|                | LF355           |     | 2   | 4   |      |

|                | LFx56, LF356B   |     | 5   | 7   | mA   |

|                | LF356           |     | 5   | 10  |      |

|                | LF357           |     | 5   | 10  |      |

## 6.7 DC Electrical Characteristics

See (1)

|                      | PARAMETER                                 |                                        | TEST C              | CONDITIONS                  | MIN | TYP              | MAX | UNIT            |

|----------------------|-------------------------------------------|----------------------------------------|---------------------|-----------------------------|-----|------------------|-----|-----------------|

|                      |                                           |                                        | т осно              | LF15x, LF25x, LF356B        |     | 3                | 5   |                 |

|                      |                                           |                                        | $T_A = 25^{\circ}C$ | LF35x                       |     | 3                | 10  |                 |

| V <sub>os</sub>      | Input offset voltage                      | R <sub>S</sub> = 50 Ω                  |                     | LF15x                       |     |                  | 7   | mV              |

|                      |                                           |                                        | Over<br>temperature | LF25x, LF356B               |     |                  | 6.5 |                 |

|                      |                                           |                                        | tomporataro         | LF35x                       |     |                  | 13  |                 |

| ΔV <sub>OS</sub> /ΔT | Average TC of input<br>offset voltage     | R <sub>S</sub> = 50 Ω                  |                     | LF15x, LF25x, LF356B, LF35x |     | 5                |     | µV/∘C           |

| ΔTC/ΔV <sub>OS</sub> | Change in average TC with $V_{OS}$ adjust | $R_{S} = 50 \ \Omega^{(2)}$            |                     | LF15x, LF25x, LF356B, LF35x |     | 0.5              |     | µV/°C<br>per mV |

|                      |                                           | $T_{J} = 25^{\circ}C^{(1)}$ (3)        |                     | LF15x, LF25x, LF356B        |     | 3                | 20  |                 |

|                      | Input offset current                      | $I_{\rm J} = 25^{\circ} C^{(1)} (0)$   |                     | LF35x                       |     | 3                | 50  | рА              |

| los                  |                                           |                                        |                     | LF15x                       |     |                  | 20  |                 |

|                      |                                           | T <sub>J</sub> ≤ T <sub>HIGH</sub>     |                     | LF25x, LF356B               |     |                  | 1   | nA              |

|                      |                                           |                                        |                     | LF35x                       |     |                  | 2   |                 |

|                      |                                           | $T_J = 25^{\circ}C^{(1)}$ (3)          |                     | LF15x, LF25x, LF356B        |     | 30               | 100 |                 |

|                      |                                           |                                        |                     | LF35x                       |     | 30               | 200 |                 |

| I <sub>B</sub>       | Input bias current                        |                                        |                     | LF15x                       |     |                  | 50  |                 |

|                      |                                           | $T_J \leq T_{HIGH}$                    |                     | LF25x, LF356B               |     |                  | 5   | nA              |

|                      |                                           |                                        |                     | LF35x                       |     |                  | 8   |                 |

| R <sub>IN</sub>      | Input resistance                          | $T_J = 25^{\circ}C$                    |                     | LF15x, LF25x, LF356B, LF35x |     | 10 <sup>12</sup> |     | Ω               |

|                      |                                           |                                        | T 05%0              | LF15x, LF25x, LF356B        | 50  | 200              |     |                 |

| •                    |                                           | $V_{\rm S} = \pm 15  \rm V,$           | $T_A = 25^{\circ}C$ | LF35x                       | 25  | 200              |     | \//\/           |

| A <sub>VOL</sub>     | Large signal voltage gain                 | $V_0 = \pm 10 V,$<br>$R_1 = 2 k\Omega$ | Over                | LF15x, LF25x, LF356B        | 25  |                  |     | V/mV            |

|                      |                                           | NL - 2 N2                              | temperature         | LF35x                       | 15  |                  |     |                 |

|                      | Outrust units and and                     | $V_S = \pm 15 \text{ V}, \text{ R}_L$  | = 10 kΩ             | LF15x, LF25x, LF356B, LF35x | ±12 | ±13              |     | Ň               |

| Vo                   | Output voltage swing                      | $V_{S} = \pm 15 V, R_{I}$              | = 2 kΩ              | LF15x, LF25x, LF356B, LF35x | ±10 | ±12              |     | V               |

(1) Unless otherwise stated, these test conditions apply:

|                                | LF15x                                                             | LF25x                                                             | LF356B                                                            | LF35x                                   |

|--------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------|

| Supply Voltage, V <sub>S</sub> | $\pm 15 \text{ V} \leq \text{V}_{\text{S}} \leq \pm 20 \text{ V}$ | $\pm 15 \text{ V} \leq \text{V}_{\text{S}} \leq \pm 20 \text{ V}$ | $\pm 15 \text{ V} \leq \text{V}_{\text{S}} \leq \pm 20 \text{ V}$ | $V_{S} = \pm 15 V$                      |

| T <sub>A</sub>                 | −55°C ≤ $T_A$ ≤ +125°C                                            | −25°C ≤ T <sub>A</sub> ≤ +85°C                                    | $0^{\circ}C \le T_A \le +70^{\circ}C$                             | $0^{\circ}C \le T_{A} \le +70^{\circ}C$ |

| T <sub>HIGH</sub>              | +125°C                                                            | +85°C                                                             | +70°C                                                             | +70°C                                   |

and  $V_{OS}$ ,  $I_B$  and  $I_{OS}$  are measured at  $V_{CM} = 0$ . The Temperature Coefficient of the adjusted input offset voltage changes only a small amount (0.5  $\mu$ V/°C typically) for each mV of (2)adjustment from its original unadjusted value. Common-mode rejection and open-loop voltage gain are also unaffected by offset adjustment.

The input bias currents are junction leakage currents which approximately double for every 10°C increase in the junction temperature, (3) T<sub>J</sub>. Due to limited production test time, the input bias currents measured are correlated to junction temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation, Pd.  $T_J = T_A + \theta_{JA}$  Pd where  $\theta_{JA}$  is the thermal resistance from junction to ambient. Use of a heat sink is recommended if input bias current is to be kept to a minimum.

## **DC Electrical Characteristics (continued)**

See (1)

|                                                    | PARAMETER                  |                       | TEST                 | MIN   | TYP  | MAX | UNIT |    |

|----------------------------------------------------|----------------------------|-----------------------|----------------------|-------|------|-----|------|----|

| V <sub>CM</sub> Input common-mode<br>voltage range |                            | V                     | LF15x, LF25x, LF356B | 11    | 15.1 |     |      |    |

|                                                    |                            | V <sub>CM, High</sub> | LF35x                | 10    | 15.1 |     | V    |    |

|                                                    | V <sub>S</sub> = ±15 V     |                       | LF15x, LF25x, LF356B |       | -12  | -11 | V    |    |

|                                                    |                            |                       | V <sub>CM, Low</sub> | LF35x |      | -12 | -10  |    |

| OMDD                                               | CMDD Common-mode rejection |                       | LF15x, LF25x, LF356B |       |      | 100 |      |    |

| CMRR                                               | CMRR ratio                 | LF35x                 |                      |       | 80   | 100 |      | dB |

| 0000                                               | Supply voltage rejection   | LF15x, LF25x, L       | 85                   | 100   |      | dB  |      |    |

| PSRR                                               | ratio <sup>(4)</sup>       | LF35x                 | 80                   | 100   |      |     |      |    |

(4) Supply Voltage Rejection is measured for both supply magnitudes increasing or decreasing simultaneously, in accordance with common practice.

## 6.8 Power Dissipation Ratings

|                                                   |                          |                      | MIN         | MAX  | UNIT |

|---------------------------------------------------|--------------------------|----------------------|-------------|------|------|

| Power Dissipation at $T_A = 25^{\circ}C^{(1)(2)}$ | I MC Dookogo (Still Air) | LF15x                |             | 560  |      |

|                                                   | LMC Package (Still Air)  | LF25x, LF356B, LF35x |             | 400  |      |

|                                                   | LMC Package              | MC Package LF15x     |             | 1200 |      |

|                                                   | (400 LF/Min Air Flow)    | LF25x, LF356B, LF35x | 1000<br>670 |      | mW   |

|                                                   | P Package                | LF25x, LF356B, LF35x |             |      |      |

|                                                   | D Package                | LF25x, LF356B, LF35x |             |      |      |

(1) The maximum power dissipation for these devices must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum available power dissipation at any temperature is P<sub>D</sub> = (T<sub>JMAX</sub> - T<sub>A</sub>) / θ<sub>JA</sub> or the 25°C P<sub>dMAX</sub>, whichever is less.

(2) Maximum power dissipation is defined by the package characteristics. Operating the part near the maximum power dissipation may cause the part to operate outside specified limits.

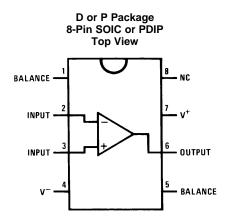

6.9 Typical Characteristics

8

www.ti.com

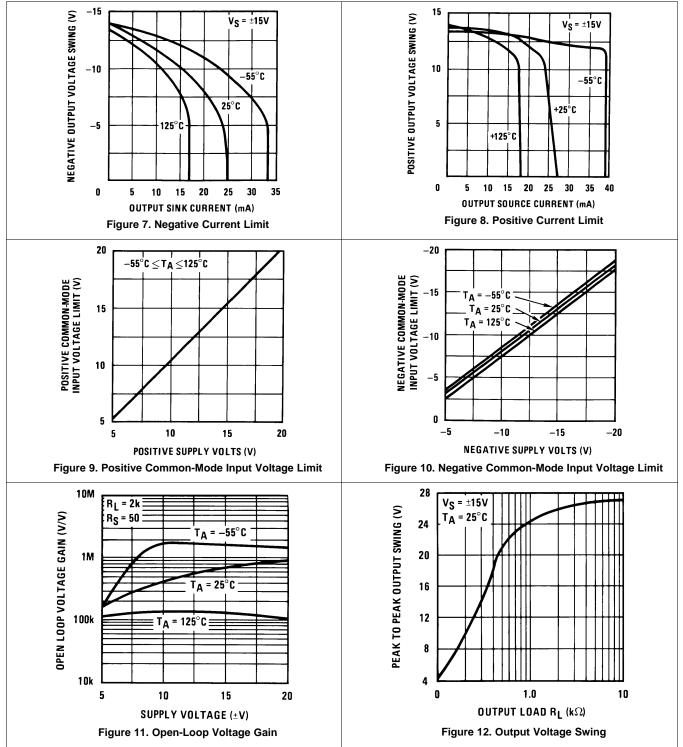

## **Typical DC Performance Characteristics (continued)**

Curves are for LF155 and LF156 unless otherwise specified.

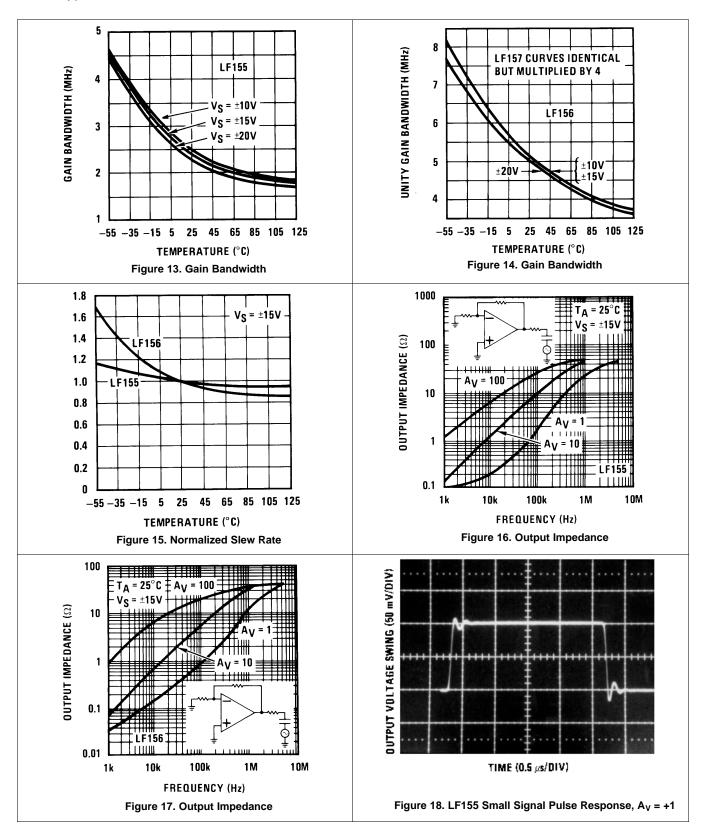

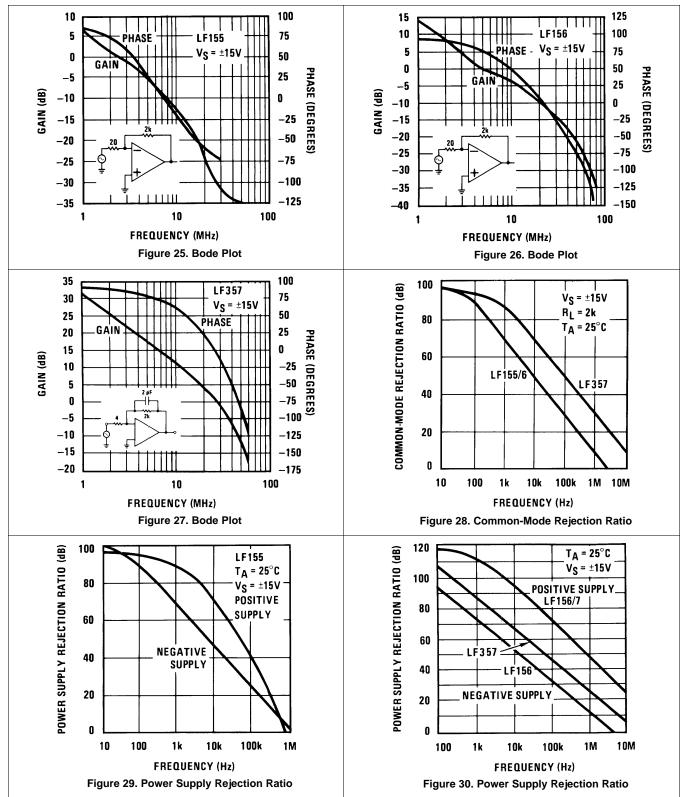

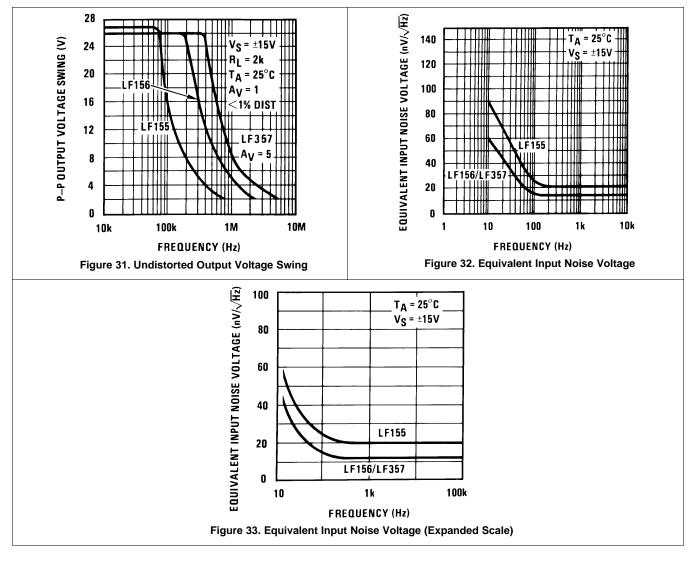

### 6.9.2 Typical AC Performance Characteristics

www.ti.com

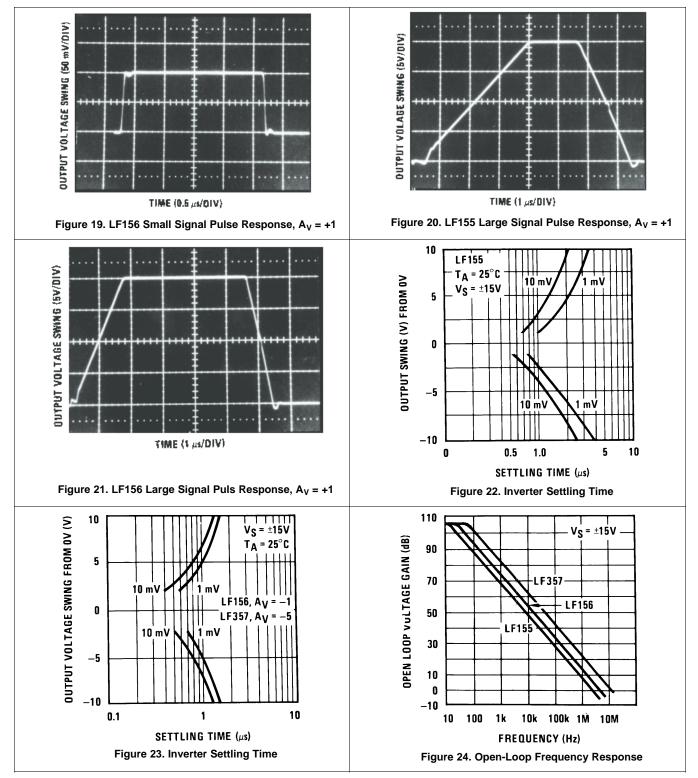

## **Typical AC Performance Characteristics (continued)**

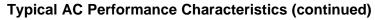

## **Typical AC Performance Characteristics (continued)**

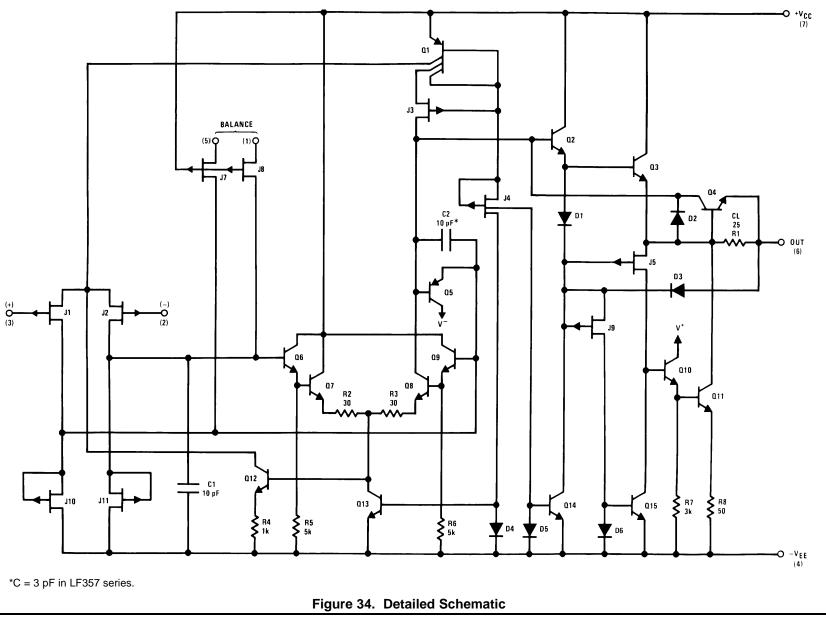

## 7 Detailed Description

## 7.1 Overview

These are the first monolithic JFET input operational amplifiers to incorporate well matched, high voltage JFETs on the same chip with standard bipolar transistors (BI-FET Technology). These amplifiers feature low input bias and offset currents, as well as low offset voltage and offset voltage drift, coupled with offset adjust which does not degrade drift or common-mode rejection. These devices can replace expensive hybrid and module FET operational amplifiers. Designed for low voltage and current noise and a low 1/f noise corner, these devices are excellent for low noise applications using either high or low source impedance.

## 7.2 Functional Block Diagram

Copyright © 2000–2015, Texas Instruments Incorporated

## 7.3 Feature Description

### 7.3.1 Large Differential Input Voltage

These are operational amplifiers with JFET input devices. These JFETs have large reverse breakdown voltages from gate to source and drain eliminating the need for clamps across the inputs. Therefore large differential input voltages can easily be accommodated without a large increase in input current. The maximum differential input voltage is independent of the supply voltages. However, neither of the input voltages should be allowed to exceed the negative supply as this will cause large currents to flow which can result in a destroyed unit.

### 7.3.2 Large Common-Mode Input Voltage

These amplifiers will operate with the common-mode input voltage equal to the positive supply. In fact, the common-mode voltage can exceed the positive supply by approximately 100 mV independent of supply voltage and over the full operating temperature range. The positive supply can therefore be used as a reference on an input as, for example, in a supply current monitor and/or limiter.

## 7.4 Device Functional Modes

The LFx5x has a single functional mode and operates according to the conditions listed in the *Recommended Operating Conditions*.

## 8 Application and Implementation

## NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

These are op amps with JFET input devices. These JFETs have large reverse breakdown voltages from gate to source and drain eliminating the need for clamps across the inputs. Therefore large differential input voltages can easily be accommodated without a large increase in input current. The maximum differential input voltage is independent of the supply voltages. However, neither of the input voltages should be allowed to exceed the negative supply as this will cause large currents to flow which can result in a destroyed unit.

Exceeding the negative common-mode limit on either input will force the output to a high state, potentially causing a reversal of phase to the output. Exceeding the negative common-mode limit on both inputs will force the amplifier output to a high state. In neither case does a latch occur since raising the input back within the common-mode range again puts the input stage and thus the amplifier in a normal operating mode.

Exceeding the positive common-mode limit on a single input will not change the phase of the output however, if both inputs exceed the limit, the output of the amplifier will be forced to a high state.

These amplifiers will operate with the common-mode input voltage equal to the positive supply. In fact, the common-mode voltage can exceed the positive supply by approximately 100 mV independent of supply voltage and over the full operating temperature range. The positive supply can therefore be used as a reference on an input as, for example, in a supply current monitor and/or limiter.

Precautions should be taken to ensure that the power supply for the integrated circuit never becomes reversed in polarity or that the unit is not inadvertently installed backwards in a socket as an unlimited current surge through the resulting forward diode within the IC could cause fusing of the internal conductors and result in a destroyed unit.

All of the bias currents in these amplifiers are set by FET current sources. The drain currents for the amplifiers are therefore essentially independent of supply voltage.

As with most amplifiers, care should be taken with lead dress, component placement and supply decoupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input to minimize pick-up and maximize the frequency of the feedback pole by minimizing the capacitance from the input to ground.

A feedback pole is created when the feedback around any amplifier is resistive. The parallel resistance and capacitance from the input of the device (usually the inverting input) to AC ground set the frequency of the pole. In many instances the frequency of this pole is much greater than the expected 3-dB frequency of the closed loop gain and consequently there is negligible effect on stability margin. However, if the feedback pole is less than approximately six times the expected 3-dB frequency a lead capacitor should be placed from the output to the input of the op amp. The value of the added capacitor should be such that the RC time constant of this capacitor and the resistance it parallels is greater than or equal to the original feedback pole time constant.

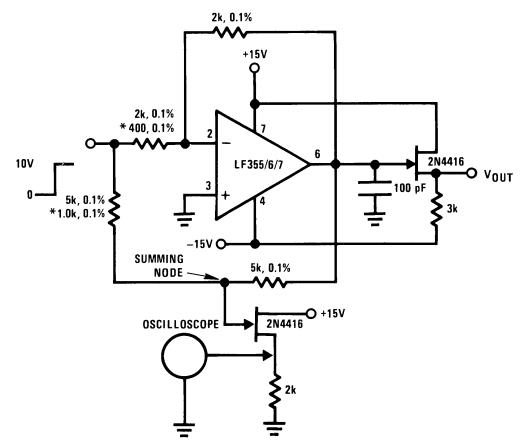

## 8.2 Typical Application

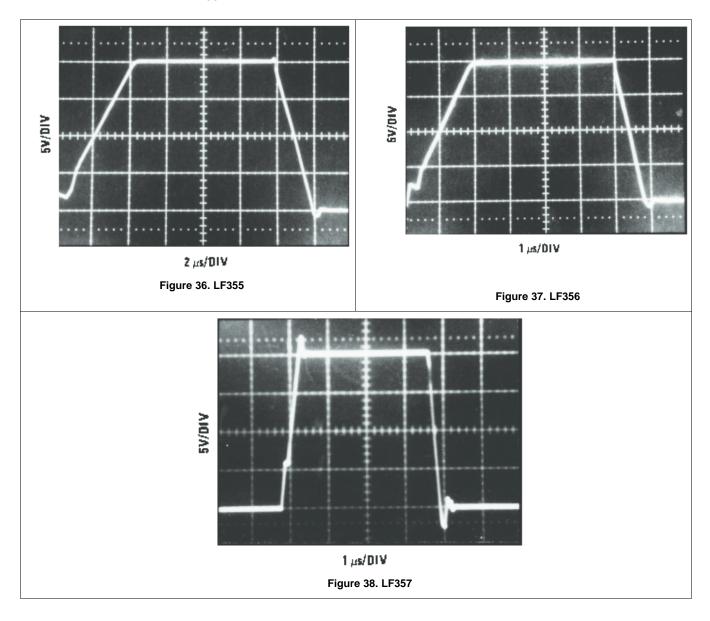

Figure 35. Settling Time Test Circuit

## 8.2.1 Design Requirements

Settling time is tested with the LF35x connected as unity gain inverter and LF357 connected for  $A_V = -5$

## 8.2.2 Detailed Design Procedure

Connect the circuit components as shown in Figure 35. In particular, use FET to isolate the probe capacitance.

Apply a 10-V step function to the input.

Use an oscilloscope to probe the circuit as shown in Figure 35.

# **Typical Application (continued)**

## 8.2.3 Application Curves

Large Signal Inverter Output, V<sub>OUT</sub> (from Settling Time Circuit)

## 8.3 System Examples

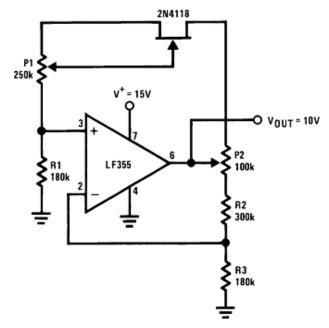

Figure 39. Low Drift Adjustable Voltage Reference

- $\Delta V_{OUT} / \Delta T = \pm 0.002\% / ^{\circ}C$

- All resistors and potentiometers should be wire-wound

- P1: drift adjust

- P2: V<sub>OUT</sub> adjust

- Use LF155 for

- Low I<sub>B</sub>

- Low drift

- Low supply current

## System Examples (continued)

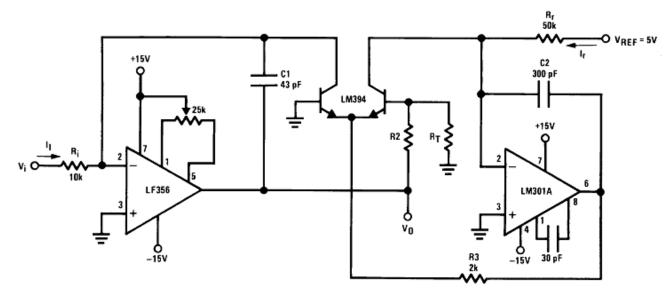

Figure 40. Fast Logarithmic Converter

- Dynamic range: 100  $\mu$ A  $\leq$  I<sub>i</sub>  $\leq$  1 mA (5 decades), |V<sub>O</sub>| = 1 V/decade

- Transient response: 3  $\mu$ s for  $\Delta I_i = 1$  decade

- C1, C2, R2, R3: added dynamic compensation

- V<sub>OS</sub> adjust the LF156 to minimize quiescent error

- R<sub>T</sub>: Tel Labs type Q81 + 0.3%/°C

$$|V_{OUT}| = \left[1 + \frac{R2}{R_T}\right] \frac{kT}{q} \text{ in } V_i \left[\frac{R_r}{V_{REF Ri}}\right] = \log V_i \frac{1}{R_i l_r} R2 = 15.7k, R_T = 1k, 0.3\%/°C \text{ (for temperature compensation)}$$

(1)

## System Examples (continued)

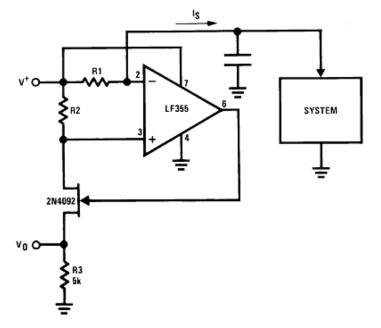

### Figure 41. Precision Current Monitor

- $V_0 = 5 \text{ R1/R2} (\text{V/mA of } I_S)$

- R1, R2, R3: 0.1% resistors

- Use LF155 for

- Common-mode range to supply range

- Low I<sub>B</sub>

- Low V<sub>OS</sub>

- Low Supply Current

## System Examples (continued)

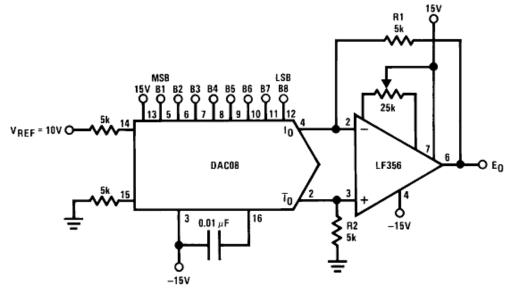

## Figure 42. 8-Bit D/A Converter With Symmetrical Offset Binary Operation

- R1, R2 should be matched within ±0.05%

- Full-scale response time: 3 µs

## Table 1. Bit Illustration of the 8-Bit D/A Converter

| Eo     | B1 | B2 | B3 | B4 | B5 | B6 | B7 | B8 | COMMENTS            |

|--------|----|----|----|----|----|----|----|----|---------------------|

| +9.920 | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | Positive Full-Scale |

| +0.040 | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | (+) Zero-Scale      |

| -0.040 | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | (−) Zero-Scale      |

| -9.920 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Negative Full-Scale |

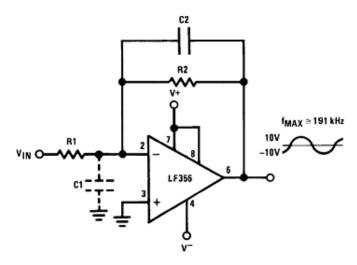

## Figure 43. Wide BW Low Noise, Low Drift Amplifier

• Power BW:  $f_{MAX} = \frac{S_r}{2\pi V_p} \cong 191 \text{ kHz}$

(2)

Parasitic input capacitance C1  $\approx$  (3 pF for LF155, LF156 and LF357 plus any additional layout capacitance) interacts with feedback elements and creates undesirable high frequency pole. To compensate add C2 such that: R2 C2  $\approx$  R1 C1.

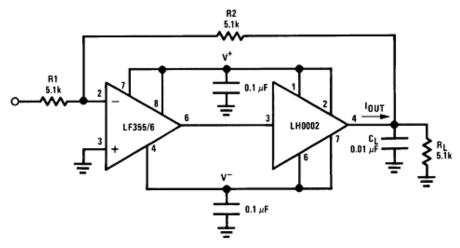

Figure 44. Boosting the LF156 With a Current Amplifier

•  $I_{OUT(MAX)} \approx 150 \text{ mA} \text{ (will drive } R_L \ge 100 \Omega)$

$$\frac{\Delta V_{OUT}}{\Delta T} = \frac{0.15}{10^{-2}} \text{ V/}\mu\text{s (with } C_{L} \text{ shown)}$$

• No additional phase shift added by the current amplifier

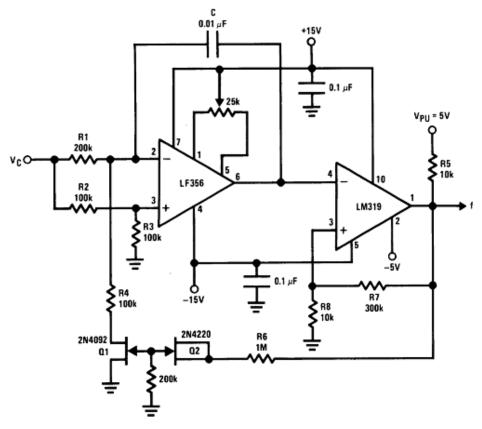

Figure 45. Decades VCO

(3)

R1, R4 matched. Linearity 0.1% over 2 decades.

$$f = \frac{V_C (R8 + R7)}{(8 V_{PU} R8 R1) C'} 0 \le V_C \le 30V, 10 Hz \le f \le 10 \text{ kHz}$$

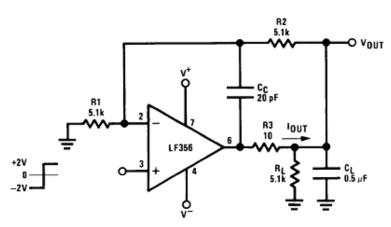

Figure 46. Isolating Large Capacitive Loads

- Overshoot 6%

- t<sub>s</sub> 10 μs

- When driving large  $C_L$ , the  $V_{OUT}$  slew rate determined by  $C_L$  and  $I_{OUT(MAX)}$ :

$$\frac{\Delta V_{\text{OUT}}}{\Delta T} = \frac{I_{\text{OUT}}}{C_{\text{L}}} \simeq \frac{0.02}{0.5} \text{ V/}\mu \text{s} = 0.04 \text{ V/}\mu \text{s} \text{ (with } C_{\text{L}} \text{ shown)}$$

$$(5)$$

$$\frac{20k}{F_{\text{T}}} = \frac{1000}{100} \text{ (b)}$$

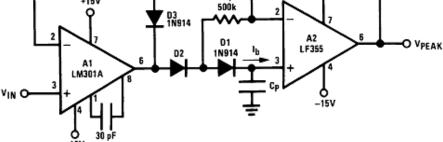

Figure 47. Low Drift Peak Detector

- By adding D1 and R<sub>f</sub>, V<sub>D1</sub> = 0 during hold mode. Leakage of D2 provided by feedback path through R<sub>f</sub>.

- Leakage of circuit is essentially I<sub>b</sub> (LF155, LF156) plus capacitor leakage of Cp.

- Diode D3 clamps V<sub>OUT</sub> (A1) to V<sub>IN</sub> V<sub>D3</sub> to improve speed and to limit reverse bias of D2.

- Maximum input frequency should be  $<< \frac{1}{2}\pi R_f C_{D2}$  where  $C_{D2}$  is the shunt capacitance of D2.

(4)

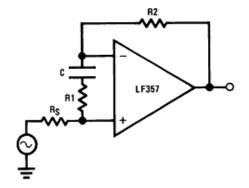

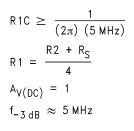

Figure 49. Inverting Unity Gain for LF157

$$R1C \ge \frac{1}{(2\pi) (5 \text{ MHz})}$$

$$R1 = \frac{R2}{4}$$

$$A_{V(DC)} = -1$$

$$f_{-3 \text{ dB}} \approx 5 \text{ MHz}$$

(7)

(6)

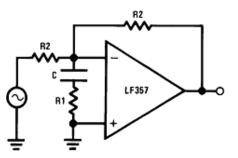

## Figure 50. High Impedance, Low Drift Instrumentation Amplifier

System V<sub>OS</sub> adjusted via A2 V<sub>OS</sub> adjust

•

Trim R3 to boost up CMRR to 120 dB. Instrumentation amplifier resistor array recommended for best accuracy and lowest drift

$$V_{OUT} = \frac{R3}{R} \left[ \frac{2R2}{R1} + 1 \right] \Delta V, V^{-} + 2V \leq V_{IN} \text{ common-mode} \leq V^{+}$$

(8)

(9)

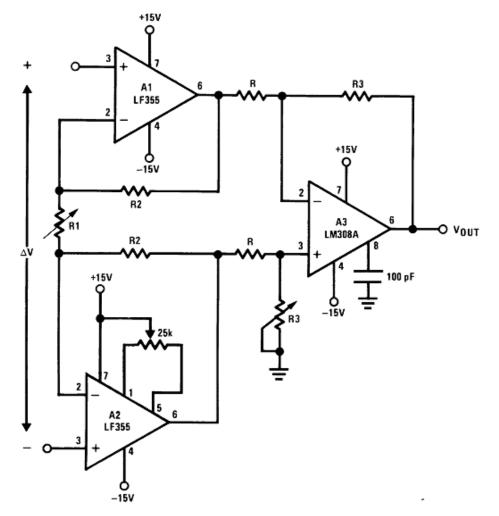

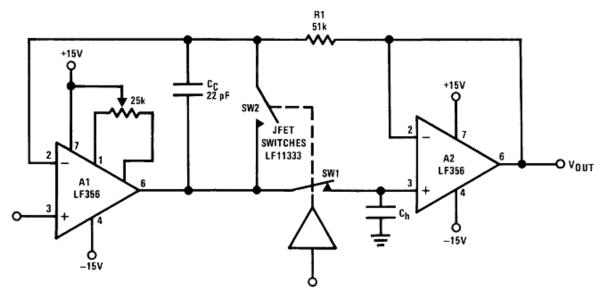

## Figure 51. Fast Sample and Hold

- Both amplifiers (A1, A2) have feedback loops individually closed with stable responses (overshoot negligible)

- Acquisition time T<sub>A</sub>, estimated by:

$$\begin{split} T_A & \cong \left[ \frac{2R_{ON}, V_{IN}, C_h}{S_r} \right] \mbox{$1/2$ provided that:} \\ V_{IN} & < 2\pi S_r \ R_{ON} C_h \ \mbox{and} \ T_A \ > \ \frac{V_{IN} C_h}{I_{OUT}(MAX)}, \ R_{ON} \ \mbox{is of $SW1$} \end{split}$$

If inequality not satisfied:  $T_A \simeq \frac{V_{IN}C_h}{20 \text{ mA}}$

- LF156 develops full S<sub>r</sub> output capability for  $V_{IN} \ge 1 V$

- Addition of SW2 improves accuracy by putting the voltage drop across SW1 inside the feedback loop

- Overall accuracy of system determined by the accuracy of both amplifiers, A1 and A2

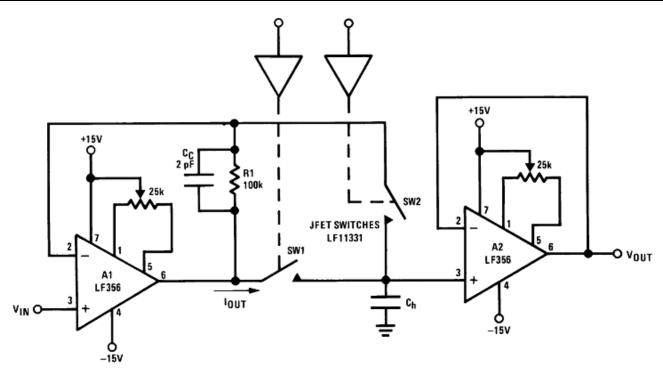

Figure 52. High Accuracy Sample and Hold

- By closing the loop through A2, the V<sub>OUT</sub> accuracy will be determined uniquely by A1.

No V<sub>OS</sub> adjust required for A2.

- T<sub>A</sub> can be estimated by same considerations as previously but, because of the added

propagation delay in the feedback loop (A2) the overshoot is not negligible.

- Overall system slower than fast sample and hold

- R1, C<sub>c</sub>: additional compensation

- Use LF156 for

- Fast settling time

- Low Vos

(10)

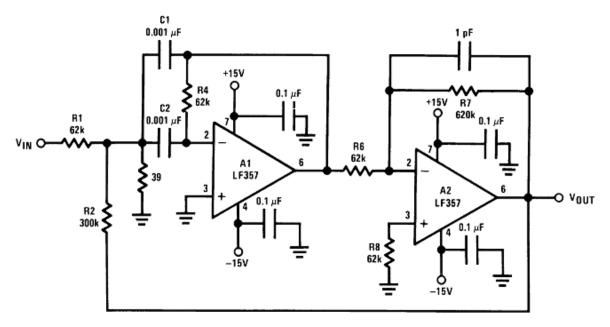

- By adding positive feedback (R2)

- Q increases to 40

- f<sub>BP</sub> = 100 kHz

$$\frac{V_{\rm OUT}}{V_{\rm IN}} = 10\sqrt{\overline{Q}}$$

- Clean layout recommended

- Response to a  $1-V_{p-p}$  tone burst: 300 µs

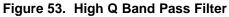

Figure 54. High Q Notch Filter

- $2R1 = R = 10 M\Omega$

- 2C = C1 = 300 pF

- Capacitors should be matched to obtain high Q

- $f_{NOTCH} = 120 \text{ Hz}, \text{ notch} = -55 \text{ dB}, \text{ Q} > 100$

- Use LF155 for

- Low  $\mathsf{I}_\mathsf{B}$

- Low supply current

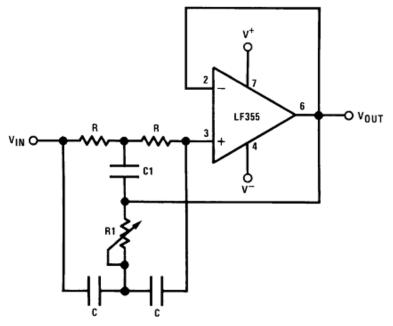

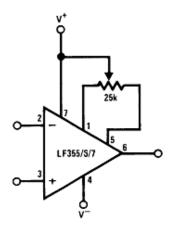

Figure 55. Vos Adjustment

- V<sub>OS</sub> is adjusted with a 25-k potentiometer

- The potentiometer wiper is connected to V<sup>+</sup>

- For potentiometers with temperature coefficient of 100 ppm/°C or less the additional drift with adjust is ≈ 0.5 µV/°C/mV of adjustment

- Typical overall drift: 5  $\mu$ V/°C ±(0.5  $\mu$ V/°C/mV of adj.)

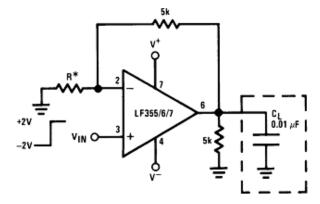

Figure 56. Driving Capacitive Loads

- <sup>\*</sup>LF15x R = 5k, LF357 R = 1.25 k

- Due to a unique output stage design, these amplifiers have the ability to drive large capacitive loads and still maintain stability. C<sub>L(MAX)</sub> ≈ 0.01 µF.

- Overshoot  $\leq$  20%, Settling time (t<sub>s</sub>)  $\approx$  5 µs

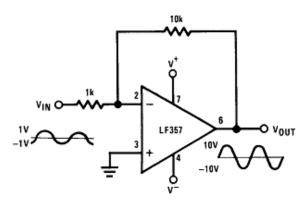

Figure 57. LF357 - A Large Power BW Amplifier

For distortion  $\leq$  1% and a 20 Vp-p V<sub>OUT</sub> swing, power bandwidth is: 500 kHz.

## 9 Power Supply Recommendations

See the *Recommended Operating Conditions* for the minimum and maximum values for the supply input voltage and operating junction temperature.

## 10 Layout

## 10.1 Layout Guidelines

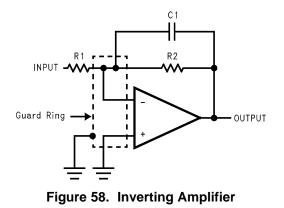

### 10.1.1 Printed-Circuit-Board Layout For High-Impedance Work

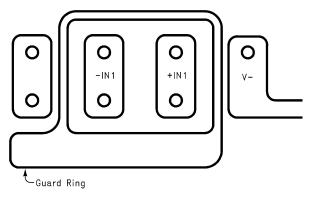

It is generally recognized that any circuit which must operate with less than 1000 pA of leakage current requires special layout of the PCB. When one wishes to take advantage of the low input bias current of the LFx5x, typically less than 30 pA, it is essential to have an excellent layout. Fortunately, the techniques of obtaining low leakages are quite simple. First, the user must not ignore the surface leakage of the PCB, even though it may sometimes appear acceptably low, because under conditions of high humidity or dust or contamination, the surface leakage will be appreciable.

To minimize the effect of any surface leakage, lay out a ring of foil completely surrounding the inputs of the LFx5x and the terminals of capacitors, diodes, conductors, resistors, relay terminals, and so forth, connected to the inputs of the op amp, as in Figure 62. To have a significant effect, guard rings must be placed on both the top and bottom of the PCB. This PC foil must then be connected to a voltage that is at the same voltage as the amplifier inputs, because no leakage current can flow between two points at the same potential. For example, a PCB trace-to-pad resistance of 10 T $\Omega$ , which is normally considered a very large resistance, could leak 5 pA if the trace were a 5-V bus adjacent to the pad of the input. If a guard ring is used and held close to the potential of the amplifier inputs, it will significantly reduce this leakage current.

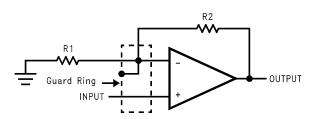

Figure 59. Noninverting Amplifier

## Layout Guidelines (continued)

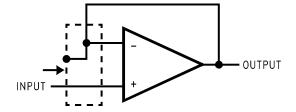

Figure 60. Typical Connections Of Guard Rings

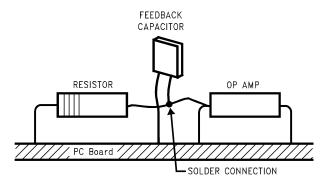

The designer should be aware that when it is inappropriate to lay out a PCB for the sake of just a few circuits, there is another technique which is even better than a guard ring on a PCB: Do not insert the input pin of the amplifier into the board at all, but bend it up in the air and use only air as an insulator. Air is an excellent insulator. In this case you may have to forego some of the advantages of PCB construction, but the advantages are sometimes well worth the effort of using point-to-point up-in-the-air wiring. See Figure 61.

(Input pins are lifted out of PCB and soldered directly to components. All other pins connected to PCB).

## Figure 61. Air Wiring

Another potential source of leakage that might be overlooked is the device package. When the LFx5x is manufactured, the device is always handled with conductive finger cots. This is to assure that salts and skin oils do not cause leakage paths on the surface of the package. We recommend that these same precautions be adhered to, during all phases of inspection, test and assembly.

## 10.2 Layout Example

## **11** Device and Documentation Support

## 11.1 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

| PARTS | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL<br>DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT &<br>COMMUNITY |

|-------|----------------|--------------|------------------------|---------------------|------------------------|

| LF156 | Click here     | Click here   | Click here             | Click here          | Click here             |

| LF256 | Click here     | Click here   | Click here             | Click here          | Click here             |

| LF356 | Click here     | Click here   | Click here             | Click here          | Click here             |

### Table 2. Related Links

## 11.2 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

## 11.3 Trademarks

BI-FET, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

## 11.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

12-Jan-2019

# PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking    | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                |              | (4/5)             |         |

| LF156 MD8        | ACTIVE | DIESALE      | Y       | 0    | 204     | Green (RoHS<br>& no Sb/Br) | Call TI          | Level-1-NA-UNLIM   | -55 to 125   |                   | Samples |

| LF156H           | ACTIVE | TO-99        | LMC     | 8    | 500     | TBD                        | Call TI          | Call TI            | -55 to 125   | ( LF156H, LF156H) | Samples |

| LF156H/NOPB      | ACTIVE | TO-99        | LMC     | 8    | 500     | Green (RoHS<br>& no Sb/Br) | Call TI          | Level-1-NA-UNLIM   | -55 to 125   | ( LF156H, LF156H) | Samples |

| LF256H           | ACTIVE | TO-99        | LMC     | 8    | 500     | TBD                        | Call TI          | Call TI            | -25 to 85    | ( LF256H, LF256H) | Samples |

| LF256H/NOPB      | ACTIVE | TO-99        | LMC     | 8    | 500     | Green (RoHS<br>& no Sb/Br) | Call TI          | Level-1-NA-UNLIM   | -25 to 85    | ( LF256H, LF256H) | Samples |

| LF356M           | NRND   | SOIC         | D       | 8    | 95      | TBD                        | Call TI          | Call TI            | 0 to 70      | LF356<br>M        |         |

| LF356M/NOPB      | ACTIVE | SOIC         | D       | 8    | 95      | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | 0 to 70      | LF356<br>M        | Samples |

| LF356MX/NOPB     | ACTIVE | SOIC         | D       | 8    | 2500    | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | 0 to 70      | LF356<br>M        | Samples |

| LF356N/NOPB      | ACTIVE | PDIP         | Р       | 8    | 40      | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-NA-UNLIM   | 0 to 70      | LF<br>356N        | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

12-Jan-2019

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

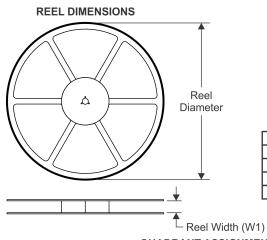

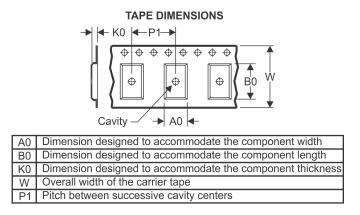

## TAPE AND REEL INFORMATION

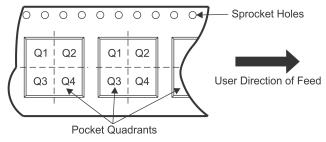

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device       | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LF356MX/NOPB | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

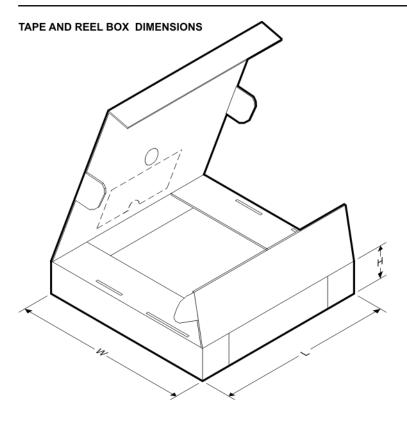

# PACKAGE MATERIALS INFORMATION

15-Sep-2018

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LF356MX/NOPB | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

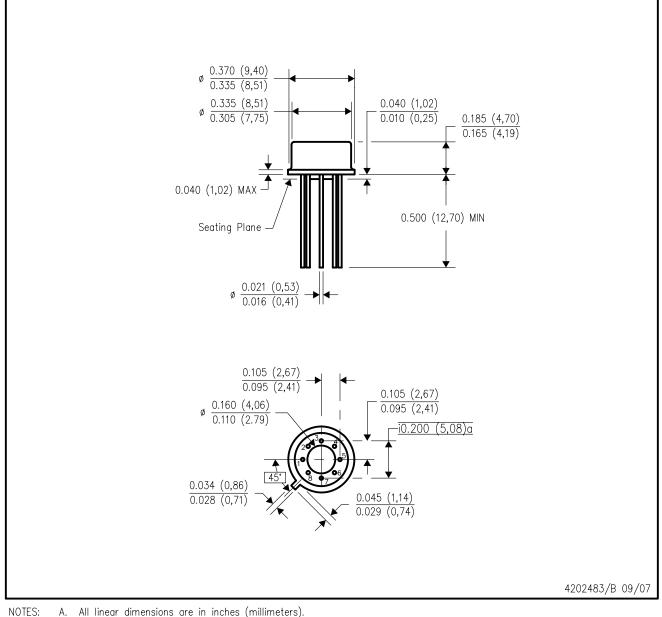

LMC (O-MBCY-W8)

# METAL CYLINDRICAL PACKAGE

- B. This drawing is subject to change without notice.

- C. Leads in true position within 0.010 (0,25) R @ MMC at seating plane.

- D. Pin numbers shown for reference only. Numbers may not be marked on package.

- E. Falls within JEDEC MO-002/TO-99.

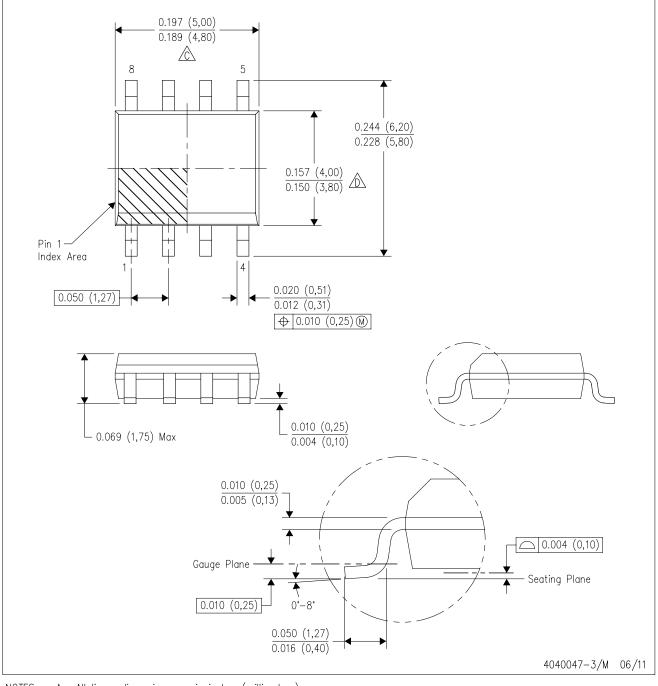

D (R-PDSO-G8)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

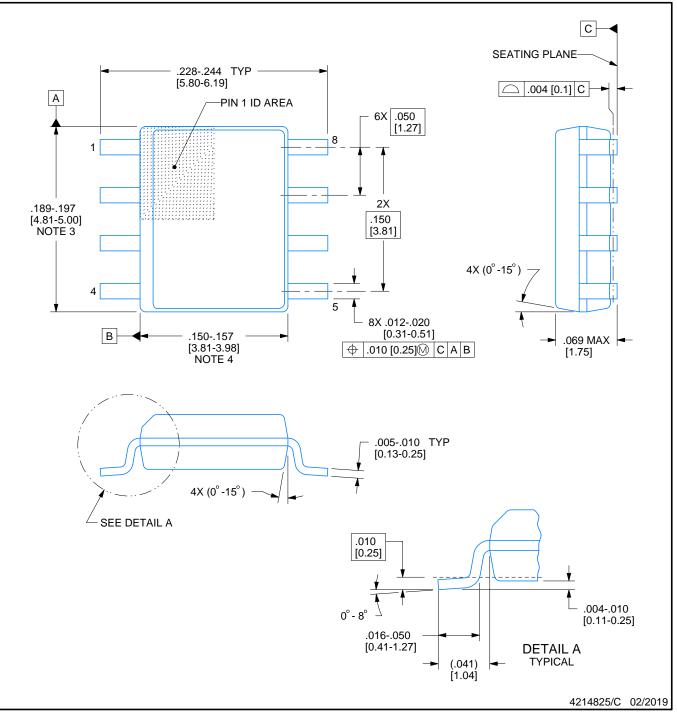

# D0008A

# **PACKAGE OUTLINE**

# SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

## NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

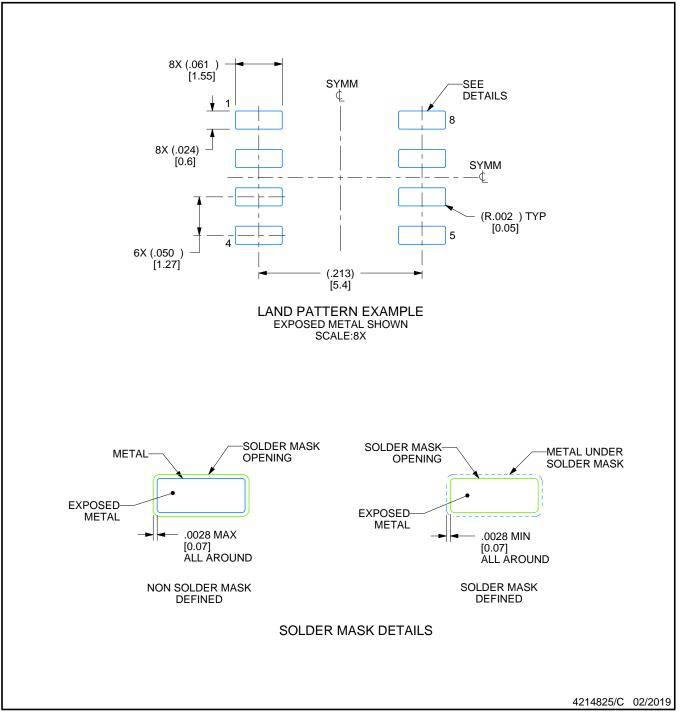

# D0008A

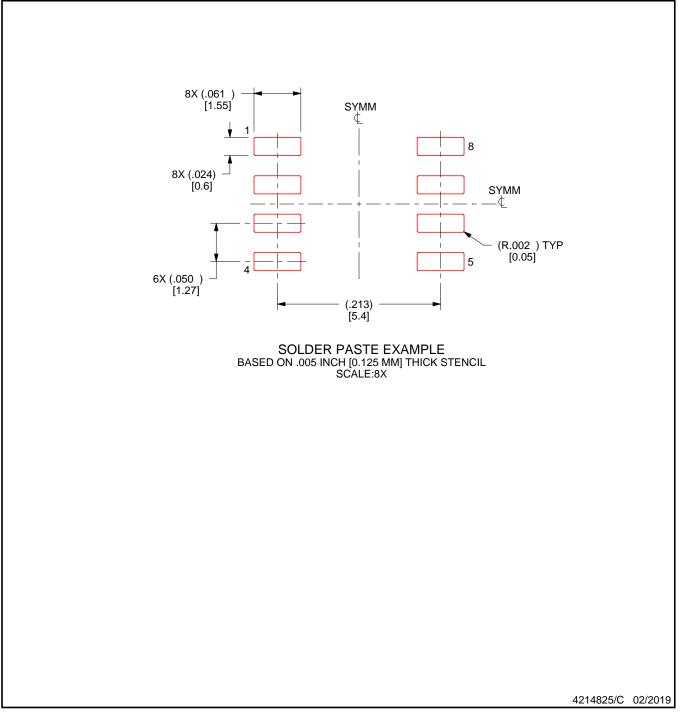

# **EXAMPLE BOARD LAYOUT**

# SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# D0008A

# **EXAMPLE STENCIL DESIGN**

# SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

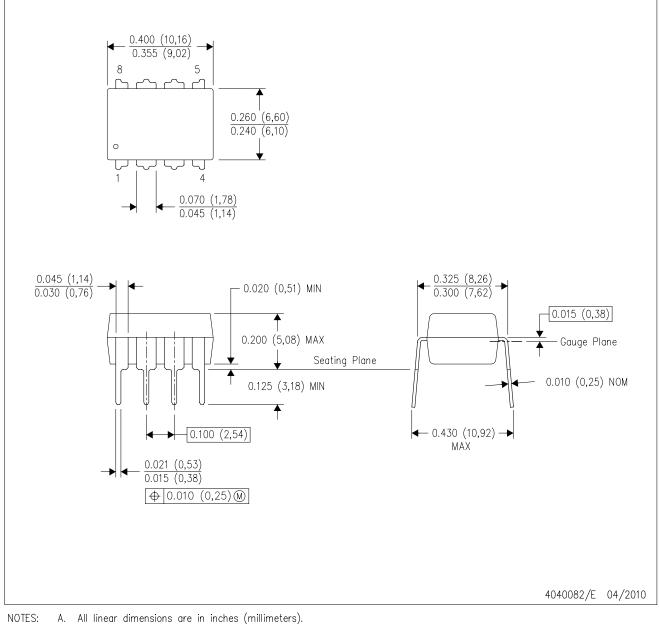

P(R-PDIP-T8)

PLASTIC DUAL-IN-LINE PACKAGE

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001 variation BA.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated